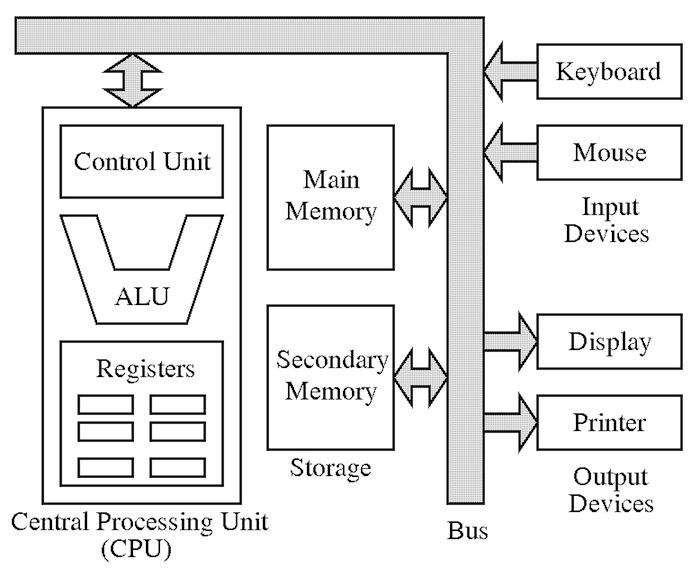

The internal components of most modern computers follow the Von Neumann architecture, which consists of five total components including three hardware components:

- The CPU which executes “code” or program instructions. It contains several components within itself. It made up of the control unit which gets instructions to execute from RAM using registers AKA instruction pointers (IP) which store the addresses of the instructions to execute. Registers are the basic data storage units for the CPU and are used to save time for the CPU so that it does not need to access RAM. The Arithmetic Logic unit or ALU executes an instruction fetched from RAM and places the results in registers or memory. The process of fetching and executing instructions continues as a program is being run.

- The main memory unit of the system (RAM) stores all the data and code instructions.

- An I/O or input/output system loads program data and instructions on the computer and initiates program execution. Output primarily stores or receives program results.

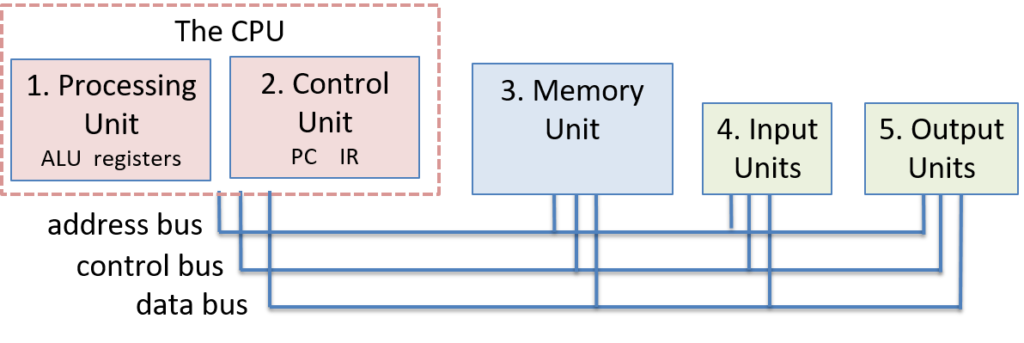

These units are connected via buses and are used by the units to send control information to one another. A bus is a communication channel that transfers binary values between the various senders and receivers of said values. It is typical for various architectures to have separate buses for sending data, memory addresses, and control instructions between the various units. The control bus is used to send control signals that notify other units of actions, the address bus to send the memory address of a read or write instruction to the memory unit, and the data bus to transfer data between units.

Further CPU Detailing

Processing Unit

VN processing units contain two parts. the ALU and the registers. The ALU performs mathematical operations such as addition, subtraction, and logical or statements. Modern ALUs perform large arithmetic operations. As outlined above these registers are data stores which hold both data and instructions and to my knowledge make no distinction between the two and are capable of holding one data word (word size has varied through time.)

Control Unit (CU)

Drives the execution of instructions by loading them from memory and giving the operands and operations through the processing unit. The control unit also has storage capability to track execution state. The program counter (PC) keeps memory addresses of the next instruction to execute, and the instruction pointer (IP) stores the instruction, loaded from memory, that is currently being executed.

Memory Unit (RAM only)

As stated above, the memory unit stores both program data and program instructions, which is a key component of the VN architecture. While the size of memory varies from system to system, a system’s Instruction Set Architecture or ISA for short limits address range that it can express. For example, 32-bit architectures typically support address space size up to 232 or 4 GB of addressable memory.

I/O units

Input devices get data from the outside world into the computer (e.g., keyboard or mouse.) Output devices do the opposite (e.g., monitor.) An example that could fall under both categories could be HD or SSD.

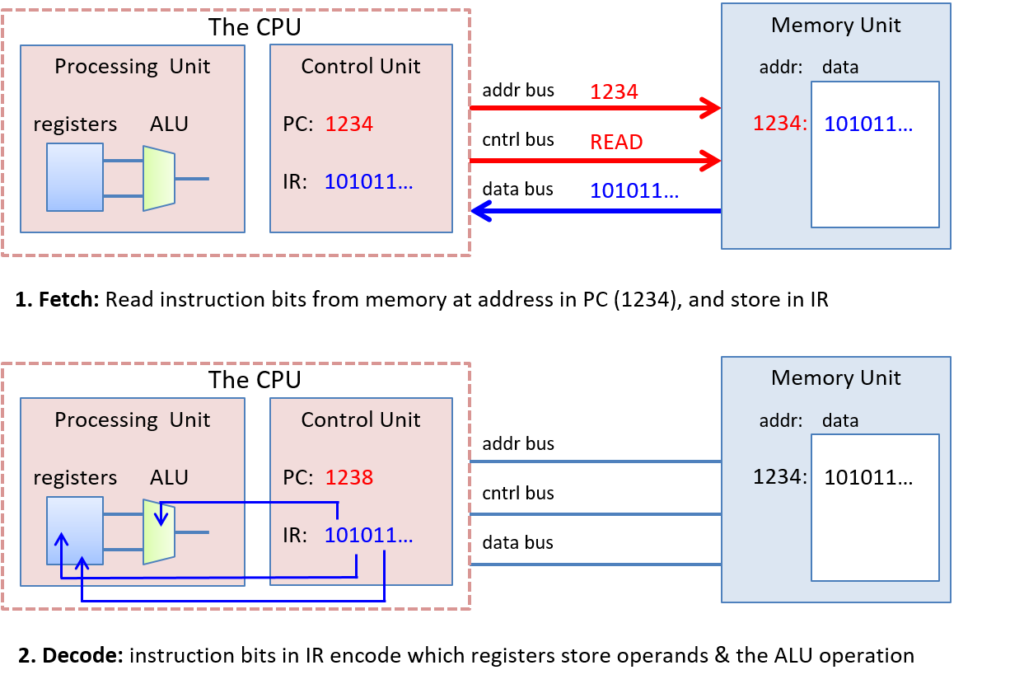

Von Neumann Execution

Similar to the way an infantryman and his rifle perform the eight cycles of function (feed-chamber-lock-fire-unlock-extract-eject-cock.) the VN machine and its components work together to perform a fetch-decode-execute-store cycle of function for task execution. This cycle starts with the first program instruction and is repeated until program exit. The control unit’s PC register contains the address of the next instruction to fetch. It then places the address on the address bus and then places a read command on the control bus to the memory unit. The MU (RAM remember?) then reads the bytes stored at the specified address and sends them to the control unit via data bus. The IP stores the instruction’s bytes received from RAM.

The next step is the CU decoding the instruction stored in the IP. The instruction bits are decoded which encode which operation to perform and the bits that encode which operation to perform and the bits that encode where the operands are located. The decoding is determined via the ISA’s definition of the encoding of its instructions. The CU also fetches the data operand values from their locations (CPU registers, memory, or encoded in the instruction bits) as input to the processing unit.

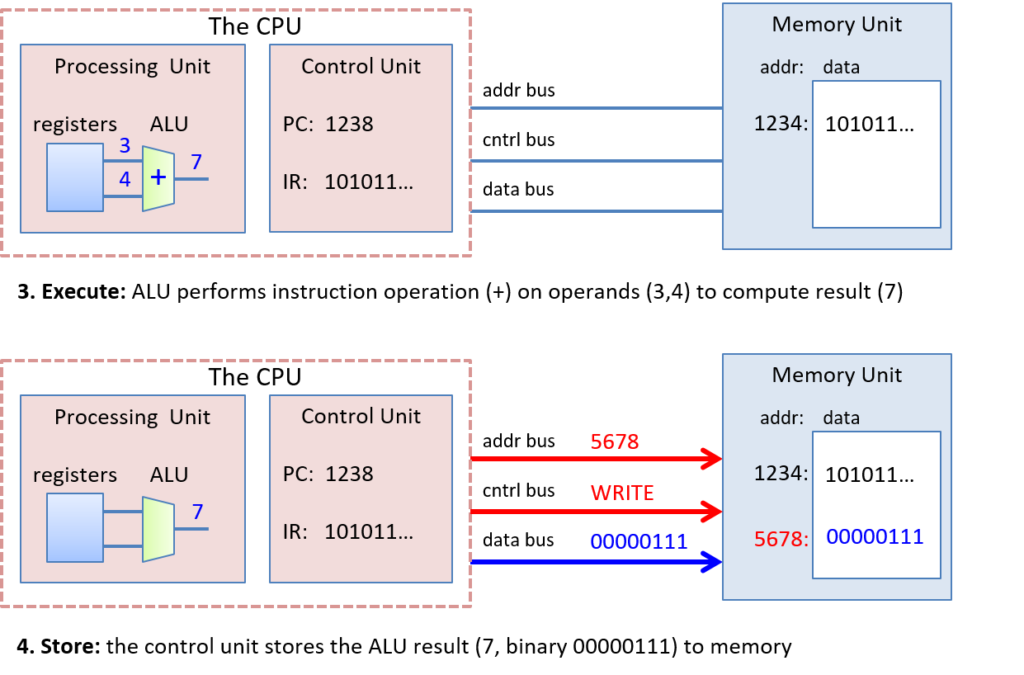

Next, the processing unit executes the instruction. The ALU performs the operation on instruction data operands.

Finally, the CU stores the results to memory. The result of the PU’s execution of the instruction is stored to memory by placing the result value on the data bus, placing the address of the storage location on the address bus, and placing a write command on the control bus. When received, the memory unit writes the value to memory at the specified address.

Below is a visual graphic to display this process.

This article was heavily aided by the following resources. Consider this a citation: